计组06

补遗

浮点数小结

例如在 1 + 4 + 3中

bias = 7

非规格浮点数的存在可以允许表示接近0的数

用1.xxx表示? \用有效位用0.xxx

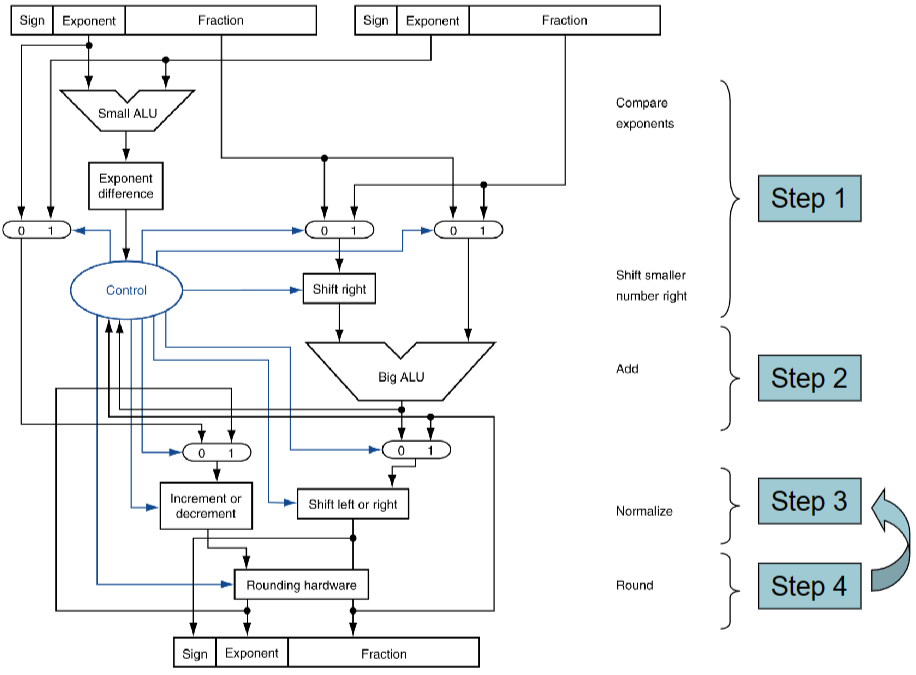

浮点数加法

先以DEC进制为例

现有两个十进制数

and

| step | detail |

|---|---|

| 1. 对阶,指数归一,小指数向大指数转化1 | |

| 2. 有效数位相加 | |

| 3. 规格化结果,检查溢出(指数) | $1.0015 \times 10^2 $ |

| 4. 舍入,向偶数舍入 |

四舍六入,中间值以下舍,中间值以上入,特判中间值,向偶数舍入

如DEC中的0.5 ,这里2是偶数38

| ori | approx |

|---|---|

| 1.6 | 2 |

| 1.4 | 1 |

| 2.5 | 2 |

| 1.5 | 2 |

BIN中,例如取小数点后两位有效位

中间值则为.xx100

| ori | approx |

|---|---|

| 1.00101 | 1.01 |

| 1.00001 | 1.00 |

| 1.11100 | 10.00舍完后重新规整化 |

| 1.10100 | 1.10 |

这里0为偶数

这里流程设计加减

浮点数乘法

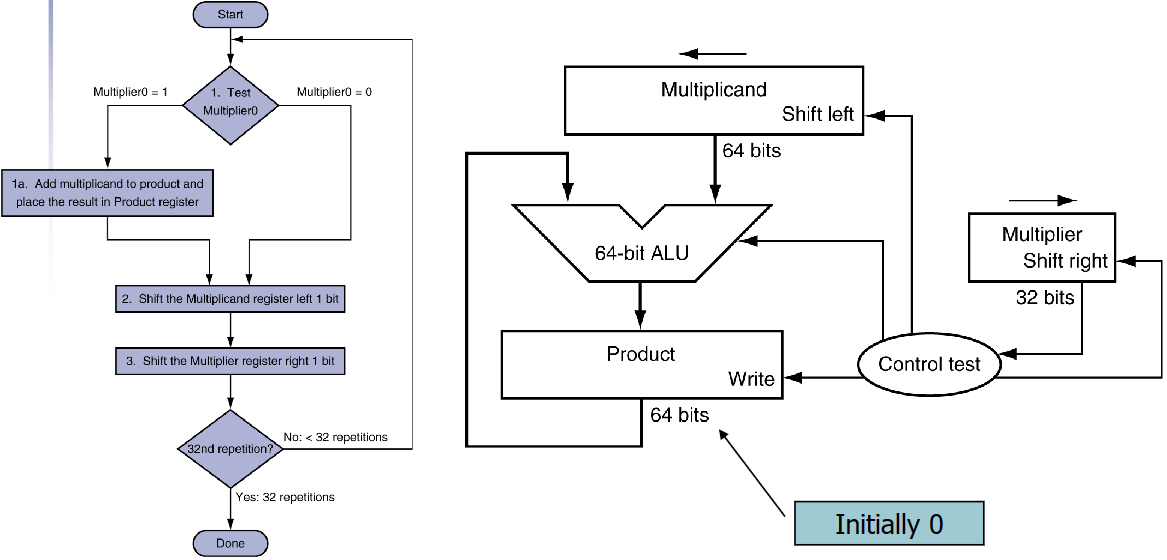

想想手工加法。

multiplicand * multiplier

这里优化可以将64bit的ALU节省到32bit的ALU

4bit两数相乘示例。

1000 * 1001

- 被乘数从右往左1stbit = 1, 这一位的积=乘数,| reg + cand = 1000

- lier 2nd bit = 0 ,积为全0 | reg先右移1位,再+0 = 0100

- lier 3rd bit = 0, 积为全0 | reg r shift ,再+0 = 0010

- lier 4th bit = 1, 积=cand | reg r shift, result = 1001 000

4位数字,4次加法运算。

再优化后 p13

mips 乘法,HI和LO

Two 32-bit registers for product

◼ HI: most-significant 32 bits

◼ LO: least-significant 32-bits

不可见

用法

mult rs,rt

multu rs,rt

64bit的结果存放在HI/LO

mfhi rd

mflo rd

load

mul rd,rs,rt

结果低32位赋值给rd

浮点数乘法

指数相加,有效数位相乘

除法

协处理器

32个单精度 reg $f0 $f1 … $f31

组合例如$f0 and $f1 可存双精度

FP instructions operate only on FP registers

◼ Programs generally don’t do integer ops on FP data,or vice versa

◼ More registers with minimal code-size impact

lwcl ldcl swcl sdcl

ldcl $f8, 32($sp)

更多操作码

◼ Single-precision arithmetic

add.s, sub.s, mul.s, div.s

◼ e.g., add.s $f0, $f1, $f6

◼ Double-precision arithmetic

add.d, sub.d, mul.d, div.d

◼ e.g., mul.d $f4, $f4, $f6

◼ Single- and double-precision comparison

c.xx.s, c.xx.d (xx is eq, lt, le, ...)

◼ Sets or clears FP condition-code bit

◼ e.g. c.lt.s $f3, $f4

◼ Branch on FP condition code true or false

bc1t, bc1f

◼ e.g., bc1t TargetLabel

代码示例

float f2c (float fahr) {

return ((5.0/9.0)*(fahr - 32.0));

}

◼ fahr in $f12, result in $f0, literals in global memory space

f2c: lwc1 $f16, const5($gp)

lwc1 $f18, const9($gp)

div.s $f16, $f16, $f18

lwc1 $f18, const32($gp)

sub.s $f18, $f12, $f18

mul.s $f0, $f16, $f18

jr $ra

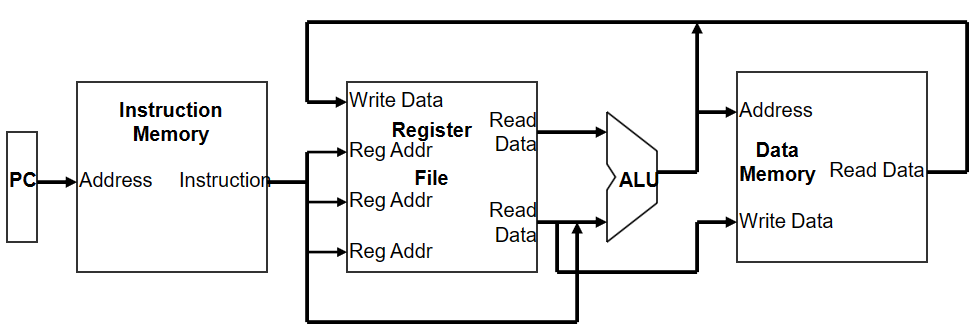

MIPS single cycle processor

取指令,

- PC M

- PC := PC + 4

执行指令

译码 -> 功能部件信号

Two types of functional units:

- elements that operate on data values (combinational)

- elements that contain state (sequential)

哈佛模型

Split memory (Harvard) model - one memory for instructions and one for data

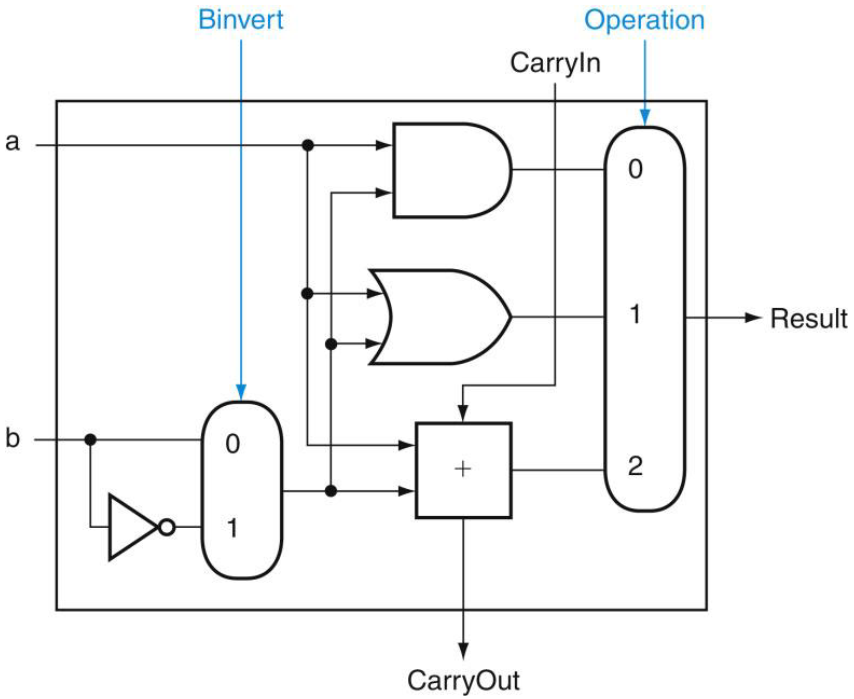

全加器,以及其执行的AND, OR, a + b, a +

其他如NOR,SLT,BEQ2

如果反过来,有效数字需要右移,高有效位的数字就无了 ↩︎

请在这里下载ppt(https://scarletborder.lanzoul.com/i7E6o1ct78ra),约ppt Chapter_04_Part01 11页 ↩︎

0 评论:

发表评论